MOS晶体管的阈值电压及输出解析

MOS晶体管MOS管

MOS管全称金属—氧化物—半导体场效应晶体管或称金属—绝缘体—半导体场效应晶体管,英文名metal oxide semiconductor,属于场效应管中的绝缘栅型,因此,MOS管有时候又称为绝缘栅场效应管。

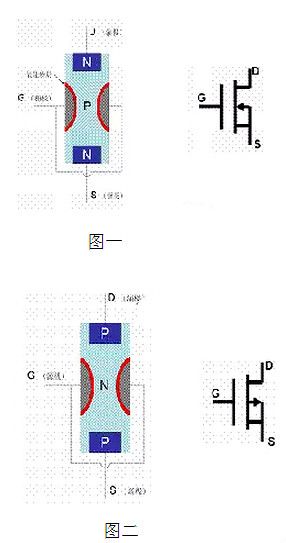

MOS管这个器件有两个电极,分别是漏极D和源极S,无论是图一的N型还是图二的P型都是一块掺杂浓度较低的P型半导体硅衬底上,用半导体光刻、扩散工艺制作两个高掺杂浓度的N+/P+区,并用金属铝引出漏极D和源极S。然后在漏极和源极之间的N/P型半导体表面复盖一层很薄的二氧化硅(Si02)绝缘层膜,在再这个绝缘层膜上装上一个铝电极,作为栅极G。这就构成了一个N/P沟道(NPN型)增强型MOS管。

MOS管工作原理与MOS晶体管的阈值电压解析

双极结晶体管是放大输入电流的微小变化以产生输出电流的大变化的晶体管。另一种类型的晶体管,称为场效应晶体管(MOSFET),将输入电压的变化转换为输出电流的变化,因此FET的增益通过其跨导来测量,跨导定义为输出电流变化与变化的比率在输入电压。电压施加到称为其栅极的输入端子,流过晶体管的电流取决于栅极电压产生的电场。在栅电极下面放置了绝缘板,因此MOSFET的栅极电流近似为零。

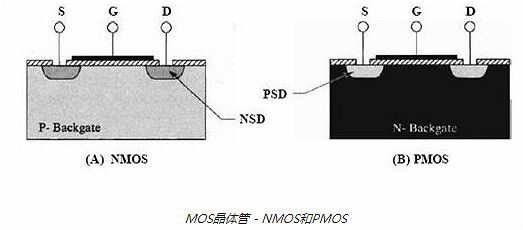

基于在绝缘层下面形成的沟道,MOS管被分类为N沟道晶体管(NMOS)和P沟道晶体管(PMOS)。两个晶体管的横截面图如图1所示。每个晶体管应具有源极,漏极,栅极和通常称为体端子的背栅。在NMOS的情况下,通过将N型掺杂剂扩散到P衬底来产生源极和栅极,反之亦然,用于PMOS。MOS晶体管的源极和漏极是可互换的,载流子流出源极并进入漏极。

NMOS晶体管 - 工作原理

下面解释NMOS管工作原理。MOS晶体管有三个操作区域。

1. 截止区域(V GS TH )

2. 三极管区域(V GS > V TH和V DS DSsat )

3. 饱和区(V GS > V TH和V DS > V DSsat )

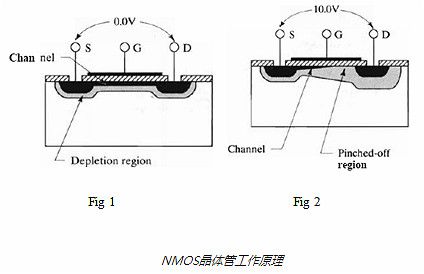

最初考虑具有V GS = 0 的Tr ,即没有施加栅极到源极电压。它类似于在源极和漏极之间背靠背连接的2个二极管。所以没有电流从源流到漏极。在源极 - 衬底,漏极 - 衬底连接处也会形成耗尽区。当 V GS 电压逐渐增加到低于阈值电压(V TH)时,栅极下方的空穴被排斥以产生耗尽区,并且在源极到漏极的栅极下它变得连续。然后V GS 增加到阈值电压即V GS > V TH 。此时,P sub中的少数载流子(电子)穿过耗尽区并到达栅极下方。此过程称为反转。栅极下方的电子数量取决于电压V GS - V TH 。

因此,由于该横向电场而产生导电通道(图1)。在源极和漏极之间建立通道后,V DS(漏极到源极电压)从0逐渐增加。当V DS 当漏极相对于源极变得更正时(图2),漏极将变为正极,子极点会反向偏置,耗尽区变宽,由于这种横向电场,电流从源极开始流动。漏极和电流随着V DS的增加而增加。因此,源极处的电位小于源极处的电位,耗尽区域在漏极附近变宽,并且沟道在此逐渐变细。

在V DS = V DSsat 时,沟道刚刚接触漏极,相应的漏极 - 源极电压称为夹断电压。高于饱和电压,电流变得恒定。载体沿着由沿着相对弱的电场推动的通道向下移动。当它们到达夹断区域的边缘时,它们被强电场吸过耗尽区域。随着漏极电压的增加,沟道两端的电压降不会增加; 相反,夹断区域变宽。因此,漏极电流达到极限并且不再增加。

MOS晶体管的阈值电压

MOS晶体管的阈值电压是刚好形成导电沟道所需的栅极 - 源极偏置电压,其中晶体管的背栅(体)连接到源极。如果栅极 - 源极偏置(V GS)小于阈值电压,则不形成沟道。给定晶体管呈现的阈值电压取决于许多因素,包括背栅极掺杂,电介质厚度,栅极材料和电介质中的过量电荷。将简要检查这些影响中的每一个。

背栅掺杂对阈值电压有重要影响。如果背栅更重掺杂,那么反转以形成通道变得更加困难。因此需要更强的电场来实现反转,并且阈值电压增加。可以通过在栅极电介质下方进行浅注入来掺杂沟道区域来调整MOS晶体管的背栅掺杂。这种类型的植入物称为阈值调节植入物(或V TH 调节植入物)。

考虑V TH 调节注入对NMOS晶体管的影响。如果植入物由受体组成,则硅表面变得更难以反转并且阈值电压增加。如果植入物由供体组成,则表面变得更容易反转并且阈值降低。如果注入足够的施主,则硅的表面实际上可以成为反掺杂的。在这种情况下,薄的N型硅层在零栅极偏压下形成永久沟道。随着栅极偏压的增加,沟道变得更强烈地反转。随着栅极偏压的减小,沟道的反转变得不那么强烈,并且在某些时候它会消失。

阈值电压也由在栅电极下方使用的电介质确定。较厚的电介质通过将电荷分开更大的距离来削弱电场。因此,较厚的电介质增加阈值电压,而较薄的电介质减小阈值电压。理论上,电介质的材料也会影响电场。实际上,几乎所有MOS晶体管都使用纯二氧化硅作为栅极电介质。可以制造极薄的SiO 2 层,具有纯度和均匀性。因此,替代的介电材料在使用中非常罕见。

栅电极材料也影响晶体管的阈值电压。在施加电压时,电场由栅极和背栅材料之间的功函数的差异产生。最常见的重掺杂多晶硅用作栅电极。通过改变掺杂,多晶硅的功函数可以改变到某种程度。在栅极氧化物中或沿着氧化物和多晶硅表面之间的界面存在过量电荷也是影响阈值电压的主要因素。这些电荷可以是电离的杂质原子,捕获的载流子或结构缺陷。这些电荷的存在将改变电场,从而改变阈值电压。如果捕获的电荷量随时间,温度或施加的偏压而变化,则阈值电压也将变化。

该NMOS晶体管的阈值电压实际上是负的。这种晶体管称为耗尽型NMOS,或简称为耗尽型NMOS。相反,具有正阈值电压的NMOS被称为增强型NMOS或增强型NMOS。大多数商业制造的MOS晶体管是增强型器件,但是有一些应用需要耗尽型器件。还可以构建耗尽型PMOS。这种器件将具有正阈值电压。

MOS晶体管的阈值电压输出特点

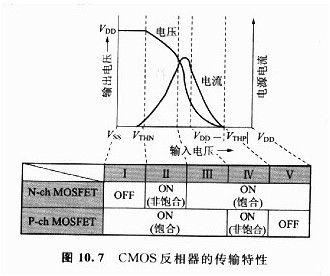

逻辑阈值电压

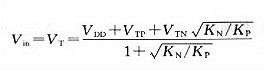

由于逻辑阈值电压是式(10.1)中的-IDS与式(10.2)中的IDS相等时的电压,所以应用这个关系能够求得Vin:

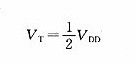

假如KN=Kp,即KN/KP=1,经过选择恰当的p沟MOS晶体管与n沟MOS晶体管的参数,可以完成|VTP|=|VTN|,那么作为反相器,当然就能够得到如下理想的关系:

实践上,这样的理想状态是不存在的。在版图设计中,经过设计恰当的p沟MOS晶体管与n沟MOS晶体管的W/L比,尽可能使VTP与VTN相等,能够得到接近1/2VDD的逻辑阈值电压。